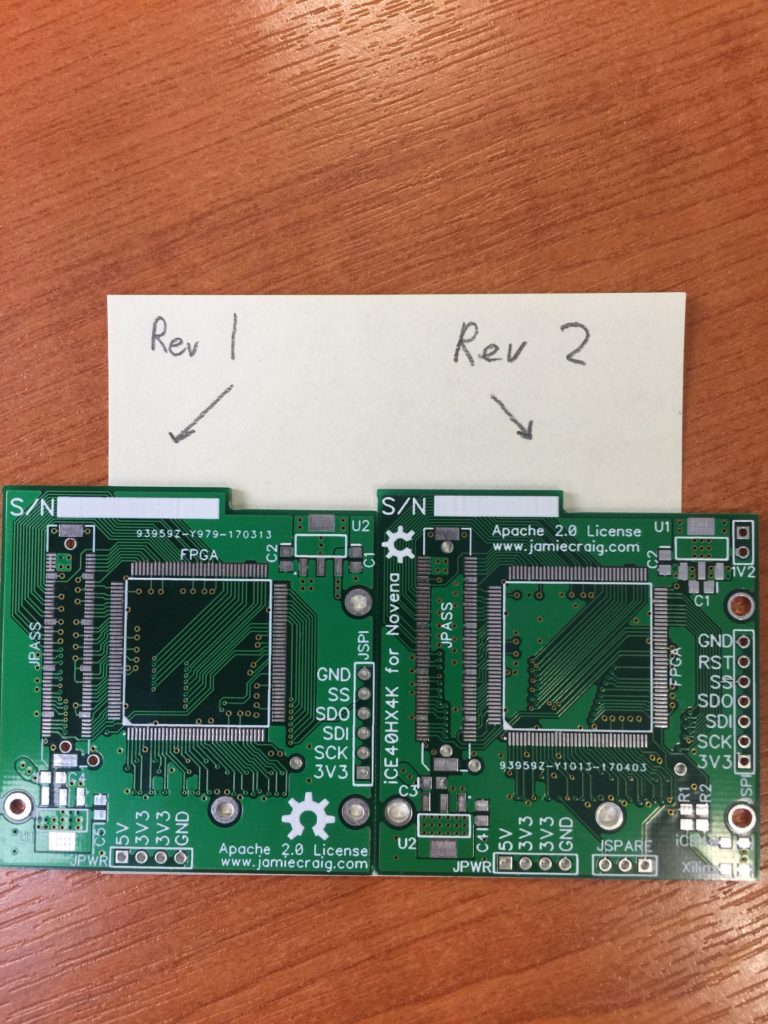

Today, I got the revision 2 boards back from DirtyPCBs, and they work well. The new pads for the FX10 connectors line up much better, and the FPGA started up first time without any trouble. The extra connectors make it a bit easier to debug, or to use the board without a Novena attached. The larger-diameter mounting holes also make it much easier to attach. At this point, I’m happy to declare these boards a success; now I just need to get some Verilog written for the bus-bridge between the Xilinx and iCE40 FPGAs.

To help anyone else writing code to run on these boards, I’ve written a spreadsheet that’ll allow you to map the iCE40 FPGA pins to the Novena standard name for them, and to the GPBB role, on both sides. It will also produce the set_io statements for IceStorm’s .pcf constraints files, which simplifies getting something up and running quickly.

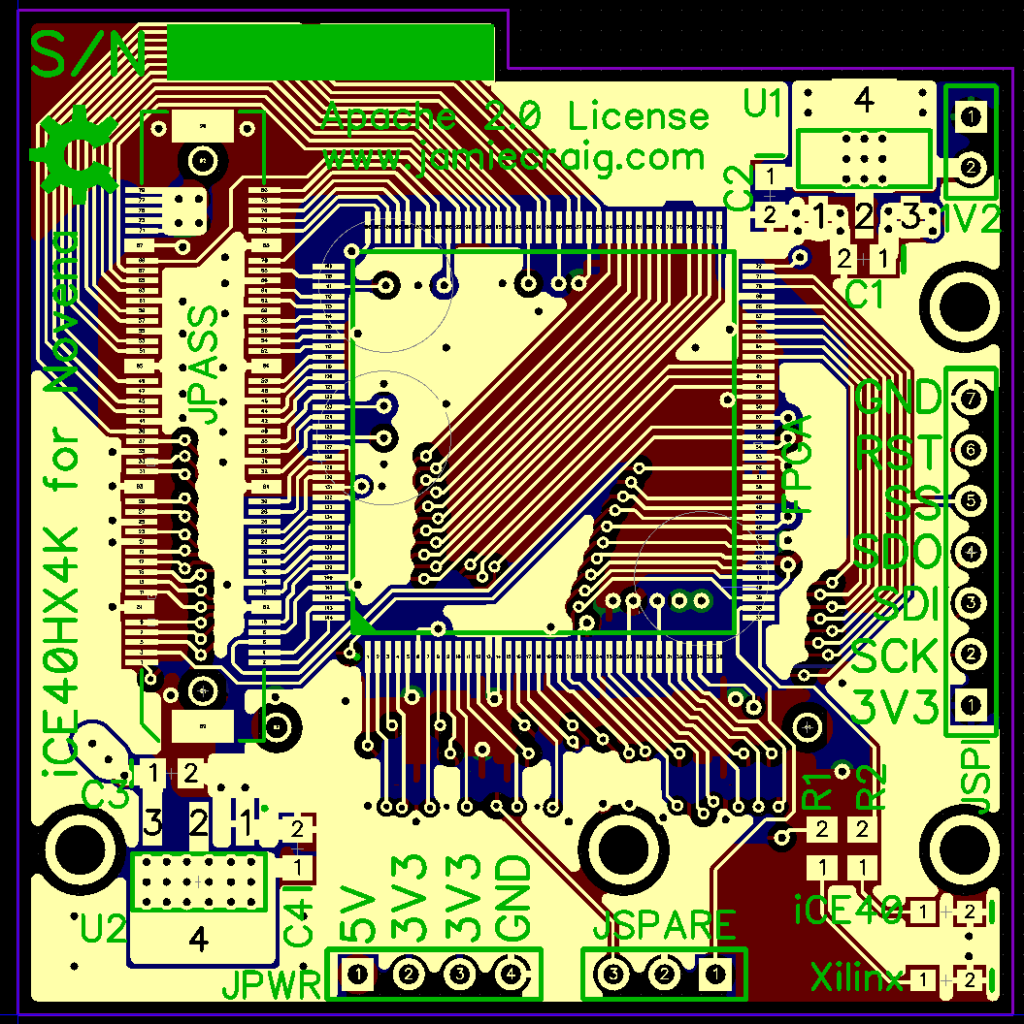

I’m not intending to manufacture any of these for general supply, but if anyone else is interested in these boards, you can get the bare PCBs from DirtyPCBs (file’s already uploaded and ready to go at this link – I’ve set up a zero cut for myself, so you’re only paying DirtyPCBs prices, no extra fees for me). The rest of the parts are listed in the BOM and are all available from both RS and Farnell – I’m sure the usual other suppliers will be able to provide something suitable as well. As the board is under the Apache 2.0 license, there’s no problem if anyone else wants to manufacture for others – feel free.

As I make progress on the bus bridge code, I’ll post it here, but in the meantime, have some blinkenlights. 🙂

Final schematics, layout, gerbers, DipTrace files, BOM, and basic demo code are all available here. – please let me know if you build one or do anything interesting with them. I’m @james_a_craig on twitter, or you can reach me on the #kosagi IRC channel on OFTC.net as MadHacker, or by email to any address at this domain.

Previously about this board: